Total Pages: 3

End Semester Examination of Semester-I, 2015

Subject: COMPUTER SCIENCE (UG)

Paper: II(L2) (Basic Electronics Lab)

Full Marks: 25

Time: 3 Hrs

The figures in the margin indicate the marks corresponding to the question

Candidates are requested to give their answers in their own word as far as practicable.

Illustrate the answers wherever necessary.

## Answer any one

Questions should be distributed on lottery basis

Experiment: 15 Marks

(Theory-5, Experiment-5, Result-5)

Viva : 5 Marks

CIA : 5 Marks

Total : 25 Marks

- 1. Study the Reverse Bias characteristics of Zener diode. Plot V/I Curve.

- Study the Forward biased characteristic of a silicon diode. Plot V/I curve. Find static and dynamic Resistance.

- 3. Design a Full-wave rectifier circuit. Find Ripple factor and Efficiency of rectifier.

- 4. Design a circuit for Load Regulation of Zener diode. Draw  $V_L/I_L$  graph. 15

- 5. Design a Regulated Power supply which will give 6 V at output. Also find % of Regulation.

- 6. Design a full wave Bridge-Rectified Circuit. Find ripple factor, % of regulation.

- 7. Design a Inverting Amplifier using IC-741 to obtain the gain of 10.

- 8. Design a non-inverting Amplifier of gain 3 using IC-741.

- 9. Design a summing amplifier using IC-741. Show the outputs of following Input voltages:

| $V_1$      | $V_2$      | V <sub>1</sub> +V <sub>2</sub> |

|------------|------------|--------------------------------|

| +1         | <b>–</b> 2 |                                |

| +1         | +2         |                                |

| <b>–</b> 2 | <b>–</b> 2 |                                |

| <b>–</b> 2 | +1         |                                |

| +2         | +2         |                                |

- 10. Design an OP-Amp Integrator Circuit. Show the Input and Output waveform.

- 11. Design an OP-AMP Differentiator Circuit. Show the Input and Output waveform. 15

15

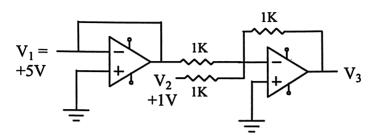

12. Design the following circuit and take the output.

Fig. 1

13. Design a Astable multivibrator and calculate the frequency and Duty Cycle.